UDC 621.382

RADIOELECTRONICS

# V.SH. MELIKYAN, A.H. SHISHMANYAN, A.S. SAHAKYAN, D.S. TRDATYAN A HIGH-LINEAR DIGITAL-TO-ANALOG CONVERTER USING THE SWITCHED-CAPACITOR TECHNIQUE

A high-linear digital-to-analog converter (DAC) with high accurate compensation is presented. The proposed architecture produces ~70% differential nonlinearity (DNL) compensation compared with the classic DAC structure. This method provides high compensation over the process, voltage and temperature (PVT) variation. The system consists of operational amplifier with negative feedback and linearity compensation circuit (using current controlled oscillator, switched-capacitor and current sources). This kind of DAC architectures can be used in System-On-Chips where data conversion needs to be implemented with high accuracy.

*Keywords:* digital-to-analog converter, switched-capacitors, current-controlled oscillator, current sources, operational amplifier.

**Introduction.** A classical digital-to-analog converter (DAC) design [1] consists of a resistor's string or current sources whose mismatch includes nonlinearity in the whole system. The process, voltage or temperature dependency of integrated elements brings errors between the target and real voltages of the DAC output. This causes a conversion error which finally increases the data error.

Compensation circuits are widely used in the process dependent architectures. In modern integrated circuits (IC), two mechanisms are mainly used to achieve the process mismatch compensation. One mechanism is using negative feedback systems, which dynamically correct the process, voltage and temperature (PVT) shifts and improve the linearity of the system. In this method the high gain amplifiers in current or voltage negative feedback are mainly used. Other mechanism uses replica of some parts of circuits with negative impacts. This helps to compensate variations and improve the system performance.

In some of the systems, these two mechanisms can be used simultaneously.

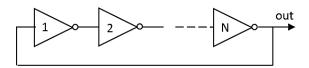

General parameters of a current-controlled oscillator (CCO) and a switched-capacitor (SC). A current controlled oscillator (CCO [2]) is a system that generates a periodical signal whose frequency depends on the input current. The important parameter of the CCO is the linear relationship between the control current and frequency. A classical CCO consists of delay cell stages (Fig. 1) whose propagation delay depends on the current, so frequency can be adjusted by changing the current.

Fig. 1. Ring Oscillator

$$f_{out} = \frac{1}{(2 \cdot \sum_{1}^{N} \frac{t_{phl} + t_{plh}}{2})}.$$

(1)

The transfer function of the CCO is:

$$f_{out} = f_0 + K_{CCO} * I_{ctrl}, \tag{2}$$

where  $f_0$  is the quiescent frequency of the oscillator and  $K_{\text{CCO}}$  denotes the gain of the CCO.

A switched-capacitor (SC) (Fig. 2) circuit is used to eliminate the resistors by replacing those elements with capacitors and switches [3]. Also, it can be used in compensation circuits using the fact that the value of the equivalent resistor (Fig. 3) can be changed by changing the frequency and capacitance.

Fig. 2. SC circuit

Fig. 3. Equivalent resistor

A capacitor charged to  $V_1$  and then to  $V_2$  during each clock period (T):

$$\Delta Q = C * (V_1 - V_2). \tag{3}$$

The equivalent average current is

$$I_{avg} = \frac{\Delta Q}{T} = \frac{C * (V_1 - V_2)}{T}.$$

(4)

For the equivalent resistor circuit

$$I_{eq} = \frac{V_1 - V_2}{R_{eq}}. (5)$$

So equating equations (4) and (5), the resistor value is:

$$R_{eq} = \frac{T}{C} = \frac{1}{f * C}. \tag{6}$$

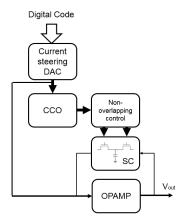

The main principle of linearization of the DAC. Compensation method is shown in Fig. 4.

Fig. 4. A block diagram of the proposed compensation method

A current steering DAC [2] controls the CCO output frequency. The replica of the DAC is also used for creating output voltage. From (6) the equivalent resistor's value is inversely proportional to frequency. Due to PVT dependency, the current of the current steering DAC can be changed and the current of the replica DAC will be changed in the same amount. That will inversely affect on  $R_{eq}$ , but as the output voltage consists of those two components, it brings good compensation dependent on various technologies.

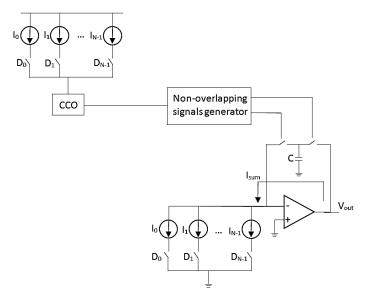

Fig. 5. The proposed DAC circuit

The working principle of the proposed DAC (Fig. 5) is as follows: changing the  $D_0, D_1, \dots D_{N-1}$  codes, the overall current increases, thus increasing the frequency of CCO, and decreasing the equivalent resistance. The output voltage is equal:

$$V_{outctrl} = I_{sum} * R_{eq}. (7)$$

The compensation mechanism can be shown by getting the final transfer function, depending on the digital binary code:

$$I_{ctrl} = \sum_{i=0}^{N} (D_i * I_i) , \qquad (8)$$

$$f_i = f_0 + K_{CCO} \sum_{i=0}^{N} (D_i * I_i) , \qquad (9)$$

$$V_{out} = \frac{\sum_{i=0}^{N} (D_i * I_i)}{C * [f_0 + K_{CCO} \sum_{i=0}^{N} (D_i * I_i)]}.$$

(10)

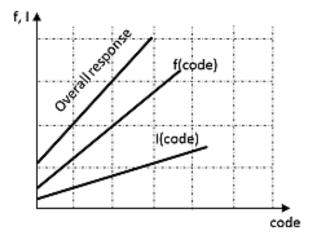

The overall response of the system is the ratio of the slopes of CCO's and DAC currents. Choosing the correct value of slopes, the overall response exhibits a clear linear response (Fig. 6).

Fig. 6. Current, frequency and overall response dependency on the code

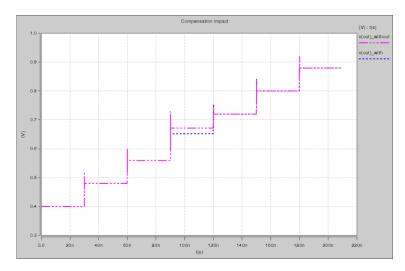

**The simulation results.** The proposed DAC architecture without compensation and with compensation has been designed with "SAED32nm" [4] library and simulated with HSPICE simulator [5]. The simulation results are shown in Fig. 7. In dotted line shown the results with compensation.

Fig. 7. Compensation impact

Below is presented a table for the 3 main bound corners for the DNL param-eter of DAC with and without compensation circuit compared with R-2R DAC [6] and segmented R-I hybrid DAC [7].

Table

|                | DNL (LSB)    |              |      |           |

|----------------|--------------|--------------|------|-----------|

| Corners        | Without      | With         | R-2R | Segmented |

|                | compensation | compensation | DAC  | R-I       |

|                |              |              | [6]  | [7]       |

| TT, 25°C       | 1,03         | 0,25         | 0,33 | 6,38      |

| $SS, -40^{O}C$ | 1,15         | 0,4          | n/a  | n/a       |

| FF, 125°C      | 1,07         | 0,12         | n/a  | n/a       |

**Conclusion.** This paper proposes a high-linear DAC which has a higher accuracy data conversion than R-2R DAC [6] and Segmented R-I hybrid [7]. Matching the current sources and their replicas, using metal capacitors in SC and operational amplifier (OPAMP) in negative feedback together, creating very high compensation of nonlinearity and improving data conversion accuracy is carried out.

The existing CCO (or VCO), OPAMP in almost all kinds of high-speed communication systems makes the use of this method very straightforward.

Compared with DACs from [6] and [7], the advantages of this DAC are high accuracy and linearity, while the drawback is the larger and higher power consumption.

#### **REFERENCES**

- Behzad Razavi. Principles of Data Conversion System Design.- 1st edition.- Wiley-IEEE Press, Dec. 12, 1994.- 272 p.

- 2. Raghunandan K.R., Viswanathan T.L., Viswanathan T.R. Linear current-controlled oscillator for analog to digital conversion // Custom Integrated Circuits Conference (CICC): IEEE Proceedings. 15-17 Sept., 2014.- P. 1-4.

- 3. **Allen Ph.E., Holberg D.R.** CMOS Analog Circuit Design (The Oxford Series in Electrical and Computer Engineering).- 3th edition.- Oxford University Press, Aug. 5, 2011.- 784 p.

- 4. https://www.synopsys.com/Community/UniversityProgram/Pages/default.aspx

- 5. HSPICE Application Manual, Synopsys Inc., 2016.

- A compact R-2R DAC for BIST applications / A. Rabal, A. Otin, I. Urriza, et al // Mixed-Signal Testing Workshop (IMSTW): 2016 IEEE 21st International.- 4-6 July, 2016.- P.1-6.

- 7. **Bill Ma, Qinjin Huang, Fengqi Yu.** A 12-bit 1.74-mW 20-MS/s DAC with resistor-string and current-steering hybrid architecture // System-on-Chip Conference (SOCC): 28th IEEE International.- 8-11 Sept., 2015.- P. 1-6.

National Polytechnic University of Armenia. The material is received 01.12.2016.

### Վ.Շ. ՄԵԼԻՔՑԱՆ, Ա.Հ. ՇԻՇՄԱՆՑԱՆ, Ա.Ս. ՄԱՀԱԿՑԱՆ, Դ.Ս. ՏՐԴԱՏՑԱՆ

#### ՓՈԽԱՆՋԱՏՎՈՂ ԿՈՆԴԵՆՍԱՏՈՐՆԵՐԻ ԿԻՐԱՌՄԱՄԲ ՄԵԾ ԳԾԱՅՆՈՒԹՅԱՄԲ ԹՎԱ-ԱՆԱԼՈԳԱՅԻՆ ՁԵՎԱՓՈՒԻՉ

Ներկայացված է մեծ գծայնությամբ և Ճշտության մեծ կոմպենսացիումով թվա-անալոգային ձևափոխիչ (ԹԱՁ)։ Առաջարկվող Ճարտարապետությունը, համեմատած դասական

ԹԱՁ-ի հետ, ապահովում է դիֆերենցիալ ոչ-գծայնության պարամետրի մինչն 70% կոմպենսացում։ Մեթոդն ապահովում է նաև մեծ կոմպենսացում գործընթացից, լարումից և ջերմաստիձանից անկախ։ Առաջարկվող համակարգը բաղկացած է բացասական հետադարձ

կապով օպերացիոն ուժեղարարից և գծայնությունը կոմպենսացնող սխեմայից (կազմված՝

հոսանքով ղեկավարվող գեներատորից, փոխանջատվող կոնդենսատորից և հոսանքի աղբյուրից)։ Այս ԹԱՁ-ը կարող է օգտագործվել այն միաբյուրեղ համակարգերում, որտեղ պահանջվում է տվյալների ձևափոխման մեծ Ճշտություն։

**Առանցքային բառեր** թվա-անալոգային ձևափոխիչ, փոխանջատվող կոնդենսատոր, հոսանքով ղեկավարվող գեներատոր, հոսանքի աղբյուր, օպերացիոն ուժեղարար**։**

## В.Ш. МЕЛИКЯН, А.Г. ШИШМАНЯН, А.С. СААКЯН, Д.С. ТРДАТЯН ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ С ВЫСОКОЙ ЛИНЕЙНОСТЬЮ С ПРИМЕНЕНИЕМ ПЕРЕКЛЮЧАЕМЫХ КОНДЕНСАТОРОВ

Представлен цифроаналоговый преобразователь (ЦАП) с высокой линейностью и большой компенсацией точности. Предлагаемая архитектура, по сравнению с классическим ЦАП, обеспечивает до ~70% компенсации дифференциальной нелинейности. Данный метод также обеспечивает большую компенсацию независимо от вариации процесса, напряжения питания и температуры. Система состоит из операционного усилителя с отрицательной обратной связью и схемы компенсации линейности (состоящей из генератора, управляемого током, переключаемых конденсаторов и источника тока). Представленный ЦАП может быть использован в системах на кристалле, где требуется более высокая точность преобразования данных.

*Ключевые слова:* цифроаналоговый преобразователь, переключаемый конденсатор, генератор, управляемый током, источник тока, операционный усилитель.