UDC 004.08:621.382.3

MICROELECTRONICS

### V.SH. MELIKYAN, E.R. KAGRAMANYAN, H.A. BABAJANYAN, R.H. MUSAYELYAN

# A FREQUENCY-TO-VOLTAGE CONVERTER WITH TWO OPERATIONAL AMPLIFIERS AND A REDUCED DELAY TIME RANGE OF THE OUTPUT SIGNAL

A new method for optimizing a frequency-to-voltage converter (FVC) circuit with an operational amplifier (op-amp) and switch capacitor is presented. By the new method of optimization, the delay time range of the output signal becomes much less. Using this method, the design obtains a higher area by 68%. It is preferable to use the optimized FVC in voltage-controlled oscillator (VCO), phase-locked loop (PLL) for the feedback connection. In the newly-designed FVC, the largest delay time range is 400 ms, when in other FVC circuits it can be more than 100 us.

Keywords: switch capacitor, op-amp, FVC, VCO.

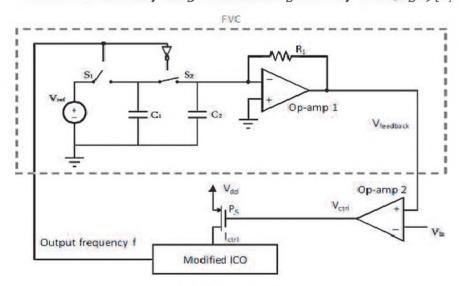

Introduction. Primary design is used in a high linearity VCO (Fig. 1) [1].

Fig. 1. VCO with a FVC

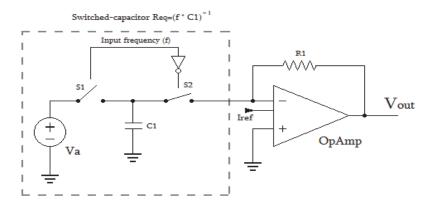

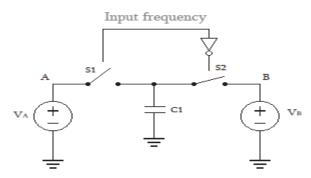

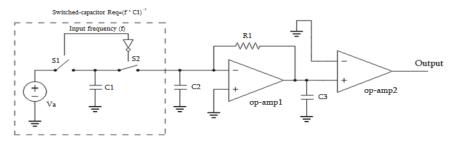

The current controlled-oscillator (ICO) used in the VCO has a problem of non-linearity of current frequency dependency. The primary FVC (Fig.2) has got high linearity having a switch capacitor (Fig.3) which works as an equivalent resistor, and an op-amp with a resistor in the feedback connection. The current

flowing through the switch capacitor is directly proportional to the input frequency, and it provides a current to the resistor in feedback connection of the op-amp. As the current is directly proportional to the input frequency, and the negative input of the op-amp is zero, the output value of FVC is also directly proportional to the input frequency. The non-linearity problem is removed by using the FVC on the feedback connection in VCO.

Fig.2. Simple FVC

Fig.3. Switch capacitor

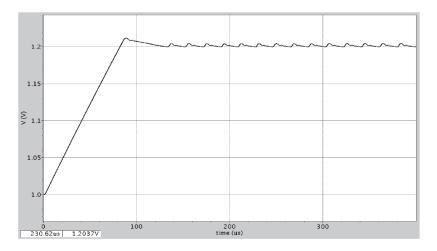

But using FVC also leads to the instability of the output signal of FVC. The stable value of the output voltage of FVC can be formed after 100 us delay time range (Fig.4).

Fig.4. Vfeedback of VCO when Vin=1.5v (characteristics are taken from [1])

For the solution, an optimization method is developed by which the delay time range will be short.

There are several methods of creating accurate FVC, for example:

- using a differentiator and a RMS-DC converter [2],

- using a R-C network, an amplifier, a rectifier and a filter [3],

- using a phase frequency detector [4],

- using a counter [5].

Comparied with these methods, the new method secures a low area for the FVC.

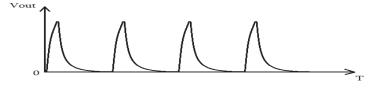

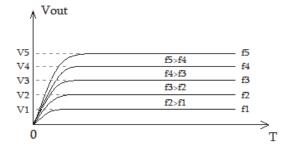

A method of FVC optimization (first step). The main problem of this circuit is that the current strength in Req is not fixed during the period. The value of the current strength that we are using in formulas is its middle value. When the S2 switch is on, the voltage of the C1 capacitor immediately increases, the current strength is big, and the output voltage is big at the beginning of the half-period. When the voltage of C1 comes close to 0, the current strength becomes much less, and the output voltage decreases. In the second half-period, when S2 is off, the output voltage completely decreases. So, the output characteristics will be as they are shown in Fig.5.

Fig.5. The output characteristics of FVC.

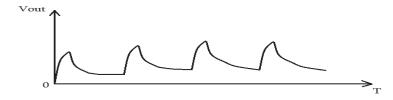

When we set the C2 capacitor in the circuit, the output voltage is becoming more balanced during the period. When S2 is on, a big current starts to flow to the input of op-amp. Some current goes to the R1 resistor and some current charges the C2 capacitor, so at the beginning of the half-period the output voltage will not be as high as without the C2 capacitor. By op-amp features, if the positive input is 0, then the negative input also must be 0, so the charge on the C2 capacitor goes to the output and at the end of the first half-period we will have a higher output voltage than in the case of not using the C2 capacitor. In the first half-periods of all the periods, when S2 is on, the output voltage increases nearly by the same size. In the second half-periods, when S2 is off, the speed of the output voltage decrease depends on the output voltage value. The higher is the output voltage at the end of the first half-period, the faster the second half-period decreases. So, the output voltage will stop on the value, by which the decreased voltage size will be equal to the increased size. So, the output characteristics by using the C2 capacitor will be as in Fig.6.

Fig.6. The output characteristics of FVC using C2

The higher the input frequency, the larger will be the increasing voltage range in the first half-period and the smaller the decreasing voltage range in the second half-period (because of the short period), the higher the output voltage will be.

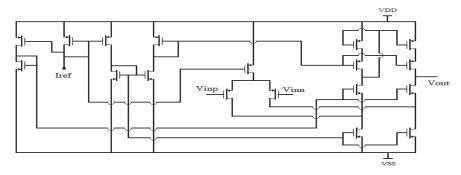

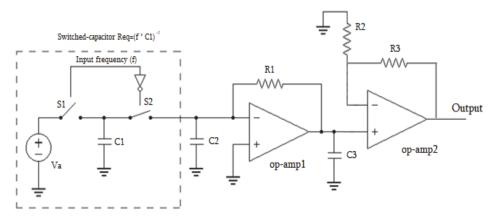

Now let's consider as R1 resistor in feedback connection. In case of high resistance of R1, the increasing voltage range of the first period will be much bigger than the decreasing voltage range, and the output voltage will reach the constant value after many periods. So, in case of a big R1 we will have a big delay time range. If we use an R1 with a low resistance, then we will have a constant output voltage very soon, but in this case, the output voltages in different frequencies will differ in a very small voltage range. To improve this, we can use the second op-amp (having a small R1). For the first and the second op-amp-s a folded cascode op-amp is chosen (Fig.7).

Fig.7. A folded cascode op-amp

If we choose a very small resistance for R1, then we will have a very small voltage range between the output voltage values for different frequencies. Also, the output voltage will be near to 0, then, if for the op-amp2 we use the output of the op-amp1 for the positive input and 0 voltage for the negative input, we will have a much increased voltage in the output of the op-amp2 than in the output of the op-amp1 (Fig.8).

So, we use the small resistance of R1 for the small delay time range and the op-amp2 to have a high output voltage. The C3 capacitor is used to smooth the dynamic transitions at the input node of the op-amp2.

Fig.8. An optimized FVC

The output characteristics of the optimized FVC are shown in Fig.9.

Fig.9. The output characteristics of the optimized FVC

The second step of the FVC optimization (with the feedback connected resistors on the op-amp2). An op-amp may have a problem of minimum output voltage. If its two inputs have the same voltage, the output voltage can be much higher than zero and, because of that, we can have a little range of the output voltage. We can fix this problem connecting two resistors by feedback connection on the op-amp2 (Fig.10).

Fig. 10. The optimized FVC (with feedback connected resistors)

As the negative input is connected to resistors, by the features of the op-amp it will have the same voltage as the positive input. The current formed on the R2 resistor will flow through the R3 resistor. The output voltage of op-amp2 will be (R3/R2) times higher than the output voltage of the op-amp1. We can choose a high value for (R3/R2) to have a high output voltage in FVC.

**Simulation results.** Here are presented the simulation results for the 32 nm technology. Simulations are performed using the HSPICE simulator. The amplitude of the input signal is 2.5 v. It changes in the [-2.5 v: 0 v] range (vddl=0, vssl=-2.5 v, vdd=2.5 v, vss=0). Knowing that Va is -2.5 v, we use a negative range for the input signal to keep the right switching of transmission gates. To the negative input of op-amp2 we give a constant voltage instead of zero. The features of the op-amps are not very perfect, and at the zero moment, the output voltage of the op-amp1 can not be very near to zero. In this case, the output voltage of the op-amp1 at the zero moment is 0.1427 v, by that, the voltage of the negative input of op-amp2 is chosen 0.1427 v to secure the linearity of the output characteristics (frequency voltage dependency) of op-amp2. R1=2.4 kom, R2=1 om and R3=250 kom. The gain of the op-amps used in this circuit is 49 dB.

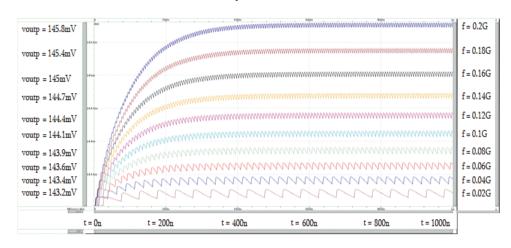

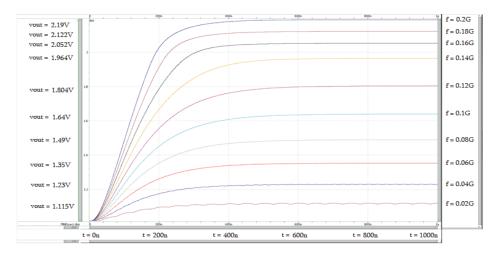

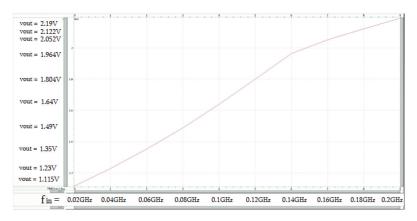

The output characteristics of the op-amps in the optimized FVC (Fig.10) are shown in Fig.11 and Fig.12. Frequency is changed from 0.02 *GHz* to 0.2 *GHz* with a 0.02 *GHz* step.

#### All characteristics are created by a HSPICE simulator.

Fig.11. The output characteristics of the op-amp1.

Fig.12. The output characteristics of the op-amp2

The dependency of the output voltage on the input frequency of the optimized FVC (with feedback connected resistors on op-amp2) is shown in Fig.13.

Fig.13. The linearity characteristics of the optimized FVC (the dependency of the output voltage on frequency). Frequency is changed from 0.02 GHz to 0.2 GHz with a 0.02 GHz step

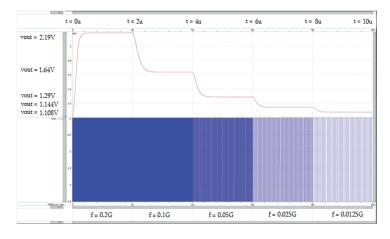

In Fig.14, output characteristics in which the input frequency is becoming twice less at the end of every 2000 n time range are presented. At the [0 - 2 u] range, the input frequency is 0.2 GHz, at [2 u - 4 u] it is 0.1 GHz, ([4 u - 6 u] - 0.05 GHz, [6 u - 8 u] - 0.025 GHz, [8 u - 10 u] - 0.0125 GHz). In the picture, we can see that the decreasing range of the output voltage also becomes nearly twice less during every 2 u time range.

Fig.14. The output characteristics with different frequencies in different time ranges.

**Conclusion.** The main advantage of the method is that we ensure the accuracy of the characteristics by providing a low voltage, and then we obtain a high voltage from it by an op-amp. In fact, the first circuit of FVC (Fig.2) has many problems in the working process. They are non-constant current, noises, delay time range, also not all features of the op-amp have high quality. The effect

of all these problems will be small if we try to get a small current and a small output voltage, and even with small values of these parameters, the linearity of the circuit is ensured. We just make a big output voltage value from small voltage using an additional op-amp, thus the operation work of the circuit is more accurate. In the FVC presented in [1], the delay time range is nearly 100 us. In the new designed FVC the delay time range is 400 ns and the area of the new design is higher by 68% than that of a simple FVC.

#### REFERENCES

- 1. **Phuong N., Low K.T., Yao L.** High Linearity Voltage-Controlled Oscillator// IEEE publisher.- Singapore, *December 11, 2009. -P.11-27.*

- 2. Simple and accurate frequency to voltage converter / A. Lorsawatsiri, W. Kiranon, V. Silaruam, W. Sangpisit, et al // IEEE publisher.- Chiang Mai, Thailand, 24 Ju ne. 2010. -P.1-3.

- 3. **Singh M., Sahu P.P.** A Wideband Linear Sinusoidal Frequency to Voltage Converter With Fast Response Time// IEEE publisher.- Tezpur, Assam, December, 2013. -P.27-35.

- A MEMS-based vacuum sensor with a PLL frequency-to-voltage converter / K. Allidina, M.A. Taghvaei, F. Nabki, P.-V. Cicek, et al // IEEE-publisher.- Montreal, Canada, January, 2010. -P.583-586.

- 5. **Garleyuk K., Pak B.H., Aksin D.Y.** A frequency to voltage converter based on an accurate pulse width modulator for frequency locked loops// IEEE-publisher.- Cusco. Peru. May, 2013. -P.1-4.

National Polytechnical University of Armenia. The materials is received on 14.02.2020.

#### Վ.Շ. ՄԵԼԻՔՅԱՆ, Է.Ռ. ԿԱԳՐԱՄԱՆՅԱՆ, Հ.Ա. ԲԱԲԱՋԱՆՅԱՆ, Ռ.Հ. ՄՈՒՍԱՅԵԼՅԱՆ

#### ԵՐԿՈՒ ՕՊԵՐԱՑԻՈՆ ՈՒԺԵՂԱՐԱՐՈՎ ԵՎ ԵԼՔԱՅԻՆ ԱՋԴԱՆՇԱՆԻ ԿԱՐՀ ՈՒՇԱՑՄԱՆ ՏԻՐՈՒՅԹՈՎ ՀԱՀԱԽՈՒԹՅՈՒՆ-ԼԱՐՈՒՄ-ՓՈԽԱԿԵՐՊԻՉ

Առաջարկվում է նոր մեթոդ՝ համախություն-լարում-փոխակերպիչի (ՀԼՓ) սխեմայի օպտիմալացման համար, երբ օգտագործվում են օպերացիոն ուժեղարար և փոխանջատ-վող կոնդենսատոր։ Օպտիմալացման նոր մեթոդի կիրառմամբ ելքային ազդանշանի ուշացման ժամանակային տիրույթը զգալիորեն փոքրանում է։ Այս մեթոդի օգտագործմամբ սխեմայի մակերեսը մեծանում 68%-ով։ Օպտիմալացված ՀԼՓ-ն նախընտրելի է օգտագործել լարումով ղեկավարվող գեներատորում, փուլահաձախականային հանգույցում՝ հետադարձ կապի համար։ Նոր նախագծված ՀԼՓ-ում մեծագույն ուշացման ժամանակային տիրույթը 400 նվ է, այնինչ այլ ՀԼՓ-ի սխեմաներում այն կարող է լինել ավելի քան 100 ս/կվ։

**Առանցքային բառեր** փոխանջատվող կոնդենսատոր, օպերացիոն ուժեղարար, 2Լ $\Phi$ , լարումով ղեկավարվող գեներատոր։

### В.Ш. МЕЛИКЯН, Э.Р. КАГРАМАНЯН, А.А. БАБАДЖАНЯН, Р.О. МУСАЕЛЯН

## ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В НАПРЯЖЕНИЕ С ДВУМЯ ОПЕРАЦИОННЫМИ УСИЛИТЕЛЯМИ И С КОРОТКИМ ДИАПАЗОНОМ ВРЕМЕНИ ЗАДЕРЖКИ ВЫХОДНОГО СИГНАЛА

Представлен новый метод оптимизации схемы преобразователя частоты в напряжение (ПЧН) с операционным усилителем и переключающимся конденсатором. Используя новый метод оптимизации, диапазон времени задержки выходного сигнала становится значительно меньше. При использовании данного метода площадь дизайна повышается на 68%. Оптимизированный ПЧН предпочтительнее использовать в генераторе, управляемом напряжением, в фазовой автоподстройке частоты для обратной связи. В новом проектированном ПЧН наибольший диапазон времени задержки выходного сигнала составляет  $400 \ nc$ , в то время как в других схемах ПЧН он может быть более чем  $100 \ mc$ .

*Ключевые слова:* переключающийся конденсатор, операционный усилитель, преобразователь частоты в напряжение (ПЧН), генератор, управляемый напряжением.