UDC 621.3.044.75 MICROELECTRONICS

DOI: 10.53297/0002306X-2023.v76.1-67

#### H.A. BABAJANYAN

# THE OUTPUT NOISE REDUCTION OF THE R-2R RESISTOR LADDER DIGITAL-ANALOG CONVERTER

A new method for reducing output noises in the R-2R resistor ladder digital-analog converter (DAC) is presented. The main reason for the output noises in R-2R resistor ladder DAC is the disadvantages and non-ideal features of the operational amplifier (Op-Amp). In case of the low numbers of the input combination there can be an output voltage without noises, because the voltage-error for the OpAmp in case of low output voltage is very small. But the low output voltage can be not the exact voltage because many times the 0 voltage on the negative input of the OpAmp forms is not clear. The high output voltage of the OpAmp can be more exact, but it will have noises because of the conflict between the voltage corresponding to the difference of the input voltages and the voltage corresponding to the current coming from the R-2R ladder. Using the new method, the output voltage of the R-2R resistor ladder DAC will be exactly in the full input combination range, and it will have almost no noise. In the primary 4-bit R-2R DAC designed in the 32 nm technology the INL (integral nonlinearity error) in case of 0000 input combination is 0.2 V, and the noiseerror in case of 0101 input combination is 0.065 V. In the optimized R-2R DAC, the maximum INL error is 0.02 V at 0010 input combination and the maximum noise-error is 0.005 V at 0001 input combination. Using the method, the area of the circuit increases by 7%. As this disadvantage is very small the new approach is very preferable to use for accurate output signal in the R-2R resistor ladder DAC.

Keywords: DAC, current mirror, Op-Amp, INL error, invertor.

**Introduction.** The DAC using R-2R resistor ladder is a simple circuit that consists of Op-Amp, resistors connected in parallel and in series in the cascaded form and the transmission gates switching the currents going from tha ladder to the OpAmp. The OpAmp can be used in the circuit in inverting and non-inverting forms. 2R ladder resistors are used as voltage dividers for the output signal depending on the input combination.

The name "ladder" means a configuration of the resistors applied within the network. A R-2R resistive ladder structure provides a means of converting digital signals to the equivalent analog output voltage. Input signals are connected to the R-2R ladder by transmission gates which are turning each branch of the ladder on

or off. The output signal is taken from the end of the ladder which is used to drive the inverting input of an OpAmp.

As transmission gates have their own resistance, the resistors need to have much more resistance than transmission gates to keep the right operation process for the DAC. But besides that, the transmission gate has got a parasitic capacitance which can import noises in the signal that must be formed in the output. For low resistance of the transmission gate, the sizes of its transistors need to be wider, so it can lead to a bigger parasitic capacitance and provide a bigger noise in the signal. But this is the smallest factor which makes noises in the output of the R-2R resistor ladder DAC. The circuit has more serious disadvantages that lead to a non-accurate output signal. The designed approach makes it possible to avoid all the dangerous features of the R-2R DAC that will import noises in the output signal.

**Literature review.** For different types of DAC, and in general for mixed-signal digital and analog circuits, there are several approaches for reducing the output noises.

For example in [1] DAC Quantization Noise Reduction is presented. In hard disk drives (HDD), the digital- analog converter (DAC) driving the voice coil motor (VCM) has a restricted accuracy. Quantization noises due to the finite precision of the DAC disturb the servo control loop and degrade its performance.

In [2] the techniques of noise improvement in data converters are presented. The data converters including ADCs and DACs work as interfaces between a DSP-based system and the physical analog circuits. The ADCs and DACs are made from basic circuit building blocks which face the design trade-offs between linearity, noise and power consumption.

In [3], an approach for reducing the noises of analog signals from PCB is presented. Noise in analog, digital systems, and analog noise in general, could be a reason of serious problems in a number of applications. Analog circuits have to deal with a range of noise sources. Some of them are unavoidable at the component and board levels.

In [4], techniques reducing noises in ADC circuits are presented. The most effective case of way for removing the noise is the use of a low-pass filter prior to the ADC. Including by-pass capacitors, and also using a ground plane will eliminate this type of noise. A third source of noise is radiated noise.

In [5], the importance of the noise reduction is presented. Most industrial environments and laboratories contain abundant electrical-noise sources which include AC power lines, radio and TV stations, and a variety of electronic

equipment. Radio stations create a high-frequency noise, when computers and also other electronic equipment generate noise in all frequency ranges.

In [6], the technique of low frequency noise reduction for linear analog integrated circuits is presented. The evaluation of VLSI technology has reached to the point where most of the transistors are integrated on a single chip. Where ICs once filled the role of subsystem components, now integrate complete systems on-a-chip by combining both digital and analog functions.

In [7], the noise reduction technique in ADC is presented. The ADC contains control circuit and a capacitive digital-to-analog-converter (CDAC). The control circuit is used for estimating the weight of the bit based on the first and second digital code. The CDAC is configured to provide the first analog signal.

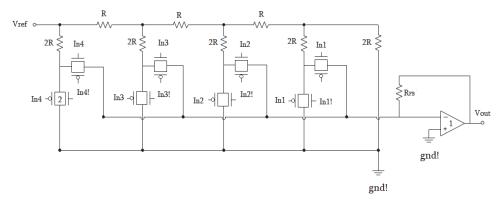

The proposed circuit of R-2R resistor ladder DAC. The method is tested on a 4-bit R-2R DAC. When first inputs are on, and the current going to the output resistor isn't so high, the OpAmp has not a big difficulty with it, and the output voltage hasn't got noises. But the instantaneous increase of the current in the resistor ladder leads to a little change in the negative input of the OpAmp, and the output signal will have an INL error at low voltages. When high bit inputs are on a big current importing a high output, voltage can make inconsistency with the gain of OpAmp, so the high output voltage will have noise problems. The primary circuit of the 4-bit R-2R resistor ladder DAC is shown in Fig.1.

Fig.1. The primary circuit of the 4-bit R-2R resistor ladder DAC (1 - OpAmp, 2 - transmission gate)

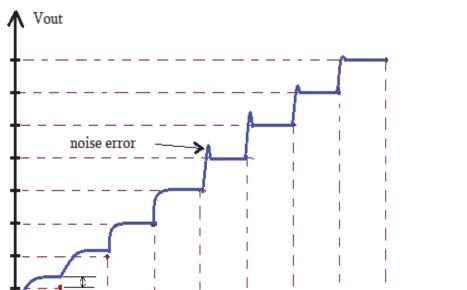

The output characteristics of the primary R-2R DAC is shown in Fig.2.

Fig.2. The output characteristics of a primary R-2R DAC

Time

INL

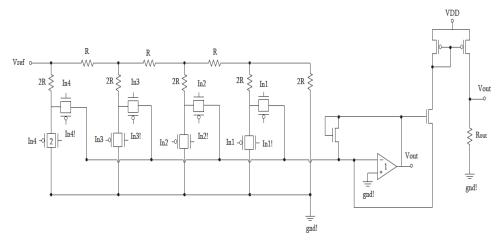

To make an accurate output signal in R-2R DAC, it is necessary to avoid big currents in the feedback loop. So, instead of the resistor in the feedback connection of OpAmp, a diode connected n-type transistor is used. The negative input of the OpAmp is connected to another n-type transistor which is connected to the first transistor with current mirror connection and also has a much bigger w-size than the first transistor. So, the current from R-2R ladder is shared between the two transistors.

The current that flows through the second transistor is much bigger than that in the first transistor as it has bigger sizes, but its current is directly proportional to the current of diode-connected transistor with a constant coefficient according to the current mirror law. The second n-type transistor is connected to another current mirror that consists of p-type transistors, which generate an accurate output voltage on the output resistor. The optimized circuit of 4-bit R-2R DAC is shown in Fig.3.

Fig.3. The optimized circuit of the 4-bit R-2R resistor ladder DAC (1 - OpAmp, 2 - transmission gate)

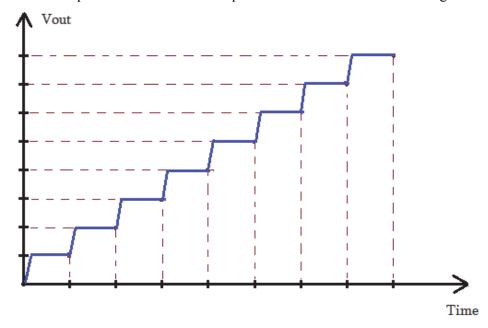

The output characteristics of the optimized R-2R DAC is shown in Fig.4.

Fig. 4. The output characteristics of the optimized R-2R DAC

**Simulation results.** The main block of a 4-bit R-2R resistor ladder DAC is designed. Simulations are performed using the HSPICE simulator (described in [8]) for a number of PVT corners including 3 main conditions (TT, FF and SS processes with respective voltage and temperature values). Here the results of the TT typical corner are presented. The circuit is designed and simulation is

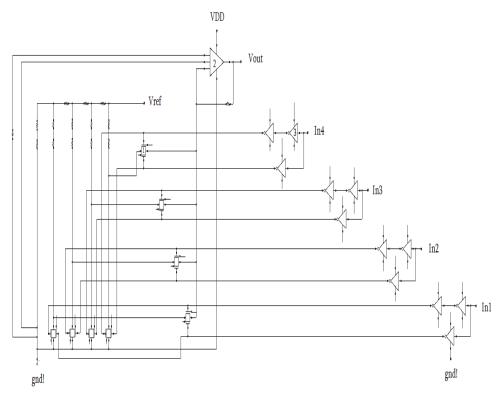

performed in the 32 nm technology. The primary circuit of the R-2R DAC designed in 32 nm technology is shown in Fig.5. Vref = -1 V and VDD = 2.5 V.

Fig. 5. The primary circuit of the 4-bit R-2R resistor ladder DAC circuit designed in 32 nm technology  $(1 - OpAmp_{,}, 2 - transmission gate, 3 - invertor)$

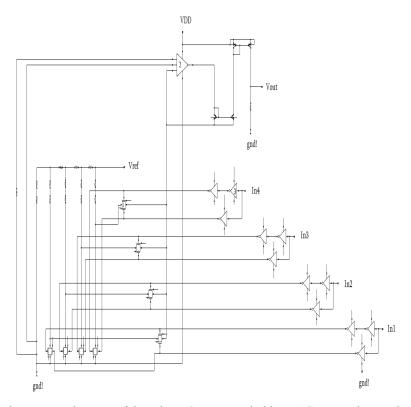

The optimized circuit of the 4-bit R-2R resistor ladder DAC is shown in Fig.6.

Fig. 6. The optimized circuit of the 4-bit R-2R resistor ladder DAC circuit designed in 32 nm technology (1 - OpAmp, 2 - transmission gate, 3 - invertor)

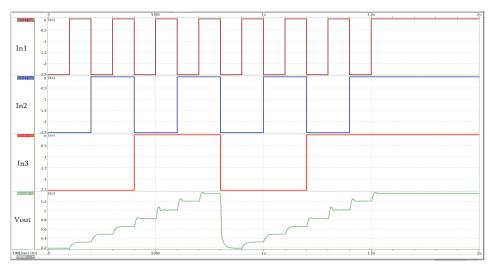

The simulation results of the primary R-2R DAC is shown in Fig.7.

Fig. 7. The simulation results of the primary 4-bit R-2R resistor ladder DAC

The simulation results of the optimized R-2R DAC is shown in Fig.8.

Fig.8. The simulation results of the optimized 4-bit R-2R resistor ladder DAC

Conclusion. A new method for the noise reduction of the R-2R resistor ladder DAC is presented. In difference with other DACs, it is very comfortable to reduce the output noises by the current mirror as the working process of the R-2R DAC is based on the output current. Experiments are carried out on the 4-bit R-2R DAC designed in the 32nm technology using OpAmp, resistors, transmission gates and invertors at the input pins. The supply voltage is 2.5 *V* and Vref which is input for the R-2R ladder is -1 *V*. At the primary R-2R DAC, the maximum INL error is 0.2 *V* and the maximum noise error is 0.065 *V*. At the optimized R-2R DAC, the maximum INL error is 0.02 *V* and the maximum noise error is 0.005 *V*. Using the method, the area increases with 7%. So, the method reduces the output noises and also fixes the INL error on the output signal.

### REFERNECES

- Lu W., Wood R., Yu M. DAC Quantization Noise Reduction for Servo Control Systems in Hard Disk Drives // American Control Conference.- Boston, Massachusetts, July 2, 2004. - P. 1147-1152.

- 2. **Zhu H.** Design Techniques to Improve Noise and Linearity of Data Converters // The Department of Electrical and Computer Engineering. April, 2016. P. 90.

- 3. **Peterson Z.** How to Reduce and Remove Noise In Analog Signals From Your PCB // Altium Designer PCB Design Software. February 15, 2021. P. 1-6.

- 4. **Baker C.** Techniques that Reduce System Noise in ADC Circuits // Microchip Technology. 2004. P. 1-2.

- 5. **Zhu H.** Noise reduction and Isolation // Measurement Computing. 2010. P. 1-10.

- 6. **Koh J**. Low-Frequency-Noise Reduction Technique for Linear Analog CMOS IC's.-Munchen technical university. November 2, 2005. 113 p.

- 7. **Chiu P., Tseng W.** Calibration and noise reduction of analog to digital converters / United States Patent, MediaTek Inc. October 6, 2015. P. 1-20.

- 8. Hspice Application Manual, Synopsys Inc. -2010. -196 p.

National Polytechnical University of Armenia. The material is received on 20.02.2023.

#### Հ.Ա. ԲԱԲԱՋԱՆՑԱՆ

### R-2R ՌԵԶԻՍՏՈՐԱՅԻՆ ՍԱՆԴՈՒՂՔՈՎ ԹՎԱ-ԱՆԱԼՈԳԱՅԻՆ ՓՈԽԱԿԵՐՊԻՉԻ ԵԼՔԱՅԻՆ ԱՂՄՈՒԿՆԵՐԻ ՆՎԱՋԱՐԿՈՒՄԸ

Ներկայացված է R-2R ռեզիստորային սանդուղքով թվա-անայոգային փոխարկիչում (ԹԱՓ) ելքային աղմուկները նվազեցնելու նոր մեթոդ։ R-2R ռեզիստորային սանդուդքով ԹԱՓ-ում ելքային աղմուկների հիմնական պատձառը օպերացիոն ուժեղարարի թերություններն ու ոչ իդեալական հատկանիշներն են։ Մուտքային կոմբինացիայի ցածր թվերի դեպքում կարող է լինել ելքային լարում՝ առանց աղմուկների, քանի որ օպերացիոն ուժեդարարի լարման սխալանքը ցածր ելքային լարման դեպքում շատ փոքր է։ Բայց ցածր ելթային լարումը կարող է լինել մուտքային կոմբինացիային ոչ համարժեր լարում, քանի որ շատ անգամ օպերացիոն ուժեղարարի բացասական մուտքի լարումը տատանվում է 0 արժեքի շուրջը։ Օպերացիոն ուժեղարարի բարձր ելքային լարումը կարող է ավելի ձշգրիտ լինել, բայց այն կունենա աղմուկներ՝ մուտքային լարումների տարբերությանը համապատասխանող ելքային լարման և R-2R սանդուղքից եկող հոսանքի լարման միջև հակասության պատճառով։ Նոր մեթոդն օգտագործելու դեպքում, R-2R ռեզիստորային սանդուղքով ԹԱՓ-ի ելքային լարումը ձշգրիտ կլինի մուտքային կոմբինացիայի ամբողջ տիրույթում և գրեթե չի ունենա աղմուկ։ Սկզբնական 4-բիթանոց, R-2R ԹԱФ-ում, որը նախագծված է 32 *նմ* տեխնոլոգիալով, ինտեգրալ ոչ գծային սխալանքը 0000 մուտքային կոմբինազիայի դեպքում 0,2 Վ է, իսկ 0101 մուտքային կոմբինացիայի դեպքում աղմուկի սխայանքը՝ 0,065 Վ: Օպտիմալացված R-2R ԹԱФ-ում առավելագույն ինտեգրալ ոչ գծային սխալանքը 0.02 Վ է 0010 մուտքային կոմբինացիայի դեպքում, իսկ աղմուկի առավելագույն սխայանքը 0001 մուտքային կոմբինացիայի դեպքում՝ 0.005 *Վ*: Օգտագործելով այս մեթոդր՝ սխեմայի մակերեսը մեծանում է 7%-ով։ Քանի որ այս թերությունը շատ փոքր է, նոր մոտեցումը շատ նախրնտրելի է օգտագործել R-2R ռեզիստորային սանդուղքով ԹԱՓ-ում՝ ձշգրիտ ելքային ազդանշան ստանալու համար։

**Առանցքային բառեր.** ԹԱՓ, հոսանքի հայելի, օպերացիոն ուժեղարար, ինտեգրալ ոչ գծայնության սխալանք, շրջիչ։

#### А.А. БАБАДЖАНЯН

## МИНИМИЗАЦИЯ ШУМА НА ВЫХОДЕ ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ С R-2R РЕЗИСТОРНОЙ ЦЕПОЧКОЙ

Представлен новый метод минимизации выходных шумов в цифроаналоговом преобразователе (ЦАП) с R-2R резисторной цепочкой. Основной причиной выходных шумов в ЦАПе с R-2R резисторной цепочкой являются недостатки и неидеальные характеристики операционного усилителя (ОУ). В случае низких цифр входной комбинации вероятно, что выходное напряжение может быть без шумов, так как погрешность напряжения для ОУ в случае низкого выходного напряжения очень мала. Но низкое выходное напряжение может быть неточным, потому что в общих случаях напряжение 0 на отрицательном входе ОУ формируется нечетко. Высокое выходное напряжение ОУ может быть более точным, но оно будет иметь шумы из-за конфликта между напряжением, соответствующим разнице входных напряжений, и напряжением, соответствующим току, поступающему от цепочки R-2R. Используя новый метод, выходное напряжение ЦАП с резисторной цепочкой R-2R будет точным во всем диапазоне комбинаций входных сигналов и почти не будет иметь шумов. В первичном 4-разрядном ЦАП R-2R, разработанном в технологии 32 нм, интегральная ошибка нелинейности при входной комбинации 0000 составляет 0,2 В, а шумовая ошибка при входной комбинации 0101 составляет 0,065 В. В оптимизированном ЦАП R-2R максимальная интегральная ошибка нелинейности составляет 0,02 В в случае 0010 входных комбинаций, а максимальная шумовая ошибка составляет 0,005 В в случае 0001 входных комбинаций. При использовании метода площадь схемы увеличивается на 7%. Поскольку этот недостаток очень мал, новый подход весьма предпочтителен для использования в ЦАП с резисторной цепочкой R-2R для получения точного выходного сигнала.

*Ключевые слова*: цифроаналоговый преобразователь, зеркало тока, операционный усилитель, ошибка интегральной нелинейности, инвертор.